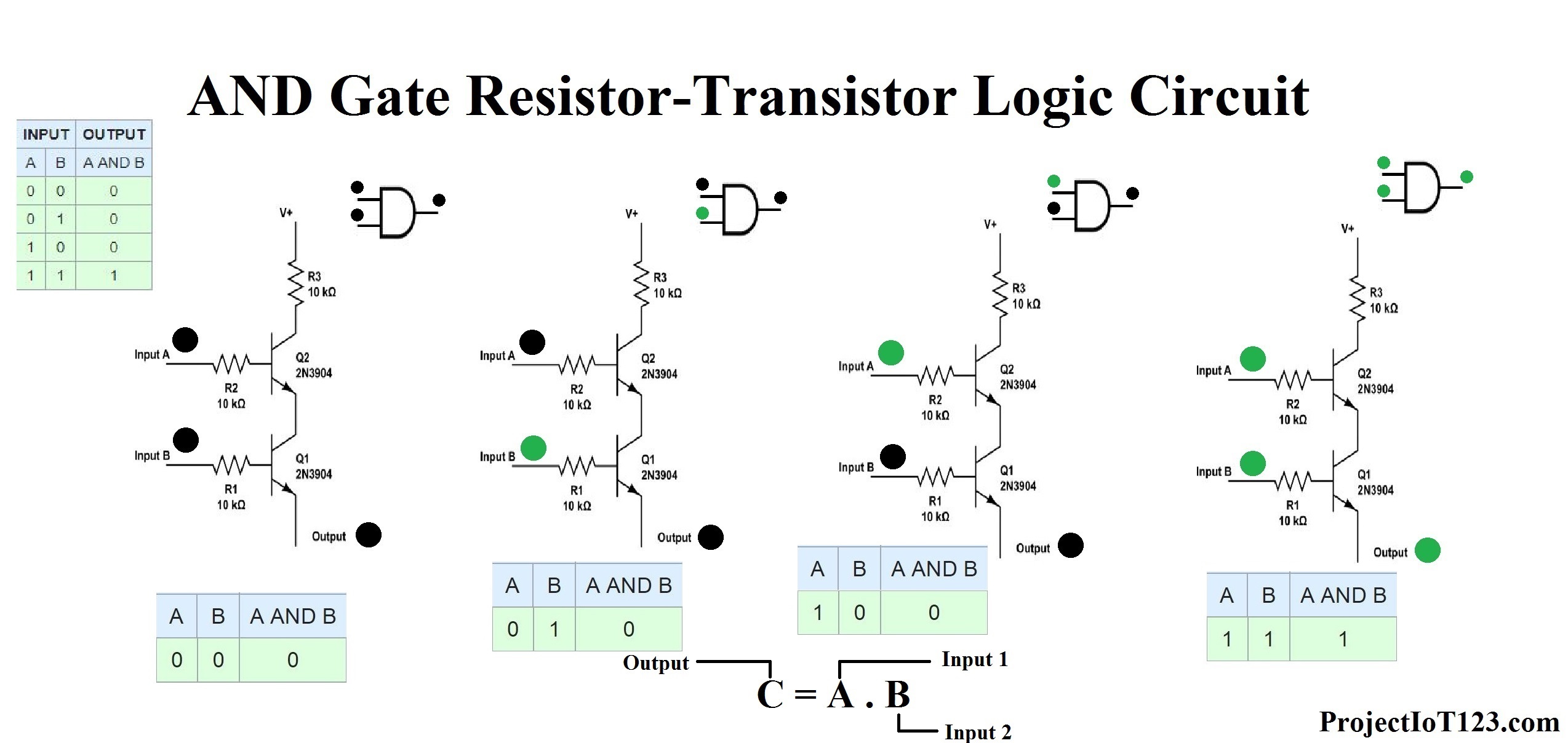

So the output is zero when both inputs are 1. The NAND gate is a quad two input of type 74H00 or 54H00. Now, as seen, the transistor \ will be turned off too. The above diagram is of a high power TTL NAND gate. When S=0, Z=A and when S=1, Z=B.The above diagram is the circuit diagram of a TTL NAND gate.įrom the diagram, we shall explain the working. Digital Logic Gates can be made from discrete components such as Resistors, Transistors and Diodes to form RTL (resistor-transistor logic) or DTL (diode-transistor logic) circuits, but today’s modern digital 74xxx series integrated circuits are manufactured using TTL (transistor-transistor logic) based on NPN bipolar transistor technology or. Here, the transmission gates selects input A or B on the basis of the value of the control signal S. Fig.5 shows the implementation of a 2:1 MUX using transmission gate logic.įig.5: Circuit diagram of a 2:1 MUX using transmission gate logic This is similar to two switches connected in. In this configuration there are two transistors connected in series. A basic circuit using any general-purpose bipolar transistor such as the BC549, BC548, or BC547, can be used to construct the AND gate.

On the other hand, C=0, places both transistors in cut-off, creating an open circuit between nodes A and B. This is a Transistor-Transistor Logic (TTL) AND Gate circuit using bipolar junction transistors. When C=1, both MOSFETs are on, allowing the signal to pass through the gate. A two-input TTL NAND gate is shown in Figure B. The multi-emitter transistor is the critical piece of technology that makes TTL logic gates possible. The transmission gate acts as a bidirectional switch controlled by the gate signal C. A smart designer realized that the DTL NAND gate of Figure B.8 could be constructed from a two-emitter transistor connected to a transistor inverter. The symbol of a transmission gate is shown below in fig.4. It is made by parallel combination of nMOS and pMOS transistors with the input at the gate of one transistor ( C) being complementary to the input at the gate () of the other. logic circuits (called gates) are used: the OR circuit, the AND circuit, and the NOT. TTL Logic Levels : For TTL circuits, the range of input. TTL (transistor-transistor logic) integrated circuits have clearly. The reduced number of devices has the additional advantage of lower capacitance.Ī transmission gate is an electronic element and good non mechanical relay built with CMOS technology. The output of a typical TTL gate under normal operation can sink currents of up to 16 mA5. The implementation of a 2:1 MUX requires 4 transistors (including the inverter required to invert S), while a complementary CMOS implementation would require 6 transistors. None of the BJT's available in high-school had multiple emitters. Rather than functioning as amplifiers, Q 1 and Q 2 are both being used as two-diode steering networks. Both transistors need to be cut-off OFF for output to be logic high. Let’s examine the following TTL circuit and analyze its operation: Transistors Q 1 and Q 2 are both arranged in the same manner that we’ve seen for transistor Q 1 in all the other TTL circuits. The TTL and STTL gates use multiple emitters on the input transistor to achieve multiple inputs. A simple two-input logic NOR gate can be assembled using a Resistor-transistor connected together as explained below with the inputs connected directly to the transistor bases.

The pass-transistor logic attempts to reduce the number of transistors to implement a logic by allowing the primary inputs to drive gate terminals as well as source-drain terminals. The LSTTL gate is essentially a 'DTL gate' with a single transistor at the input and two diodes and a resistor used to perform the logic function. Design of a 2:1 MUX using pass-transistor logic Fig.3 shows how a 2:1 MUX is implemented using a pass-transistor logic.įig.3.

A multiplexer of 2 n inputs has n selected lines, are used to select which input line to send to the output.įig.1: The schematic diagram, boolean equation and the truth table of a 2:1 multiplexer with inputs A and B, select input S and the output Z.įigure 2 shows how a 4:1 MUX can be constructed out of two 2:1 MUXs.įig.2: Implementation of 4:1 MUX using 2:1 MUXsĪ multiplexer can be designed using various logics. Both transistors must be saturated ON for an output at Q. The aim of this experiment is to design and plot the characteristics of a 4x1 digital multiplexer using pass transistor and transmission gate logic.Ī multiplexer or mux is a combinational circuits that selects several analog or digital input signals and forwards the selected input into a single output line. A simple 2-input AND gate can be constructed using RTL Resistor-transistor switches connected together as shown below with the inputs connected directly to the transistor bases.

0 Comments

Leave a Reply. |

Details

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed